# The efficient path to increased performance

**Intel® Cluster Studio XE 2013** combines proven cluster and performance profiling tools with advanced threading and memory correctness analysis to boost HPC application performance and reliability.

- Industry-leading Intel® MPI Library: New levels of performance, scalability and flexibility for cluster applications on Intel® platforms

- Intel® C, C++, and Fortran compilers:

Built-in optimization technologies and multithreading support

- > Intel® VTune™ Amplifier XE and Intel® Inspector XE: Efficient thread and memory analysis

- > Intel® Cilk™ Plus and Intel® Threading Building Blocks: Support open, standard parallel programming models

SCALE HPC APPLICATIONS FORWARD, FASTER

# CONTENTS

| Letter from the Editor                                                                                                                                                                    |                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| When Complex Is the Baseline, BY JAMES REINDERS                                                                                                                                           | 4                                                        |

| Shedding Light on Cluster Performance with LAMMPS, BY WALTER SHANDS.                                                                                                                      | ing Light on Cluster Performance with LAMMPS,  ER SHANDS |

| Highlights the features of Intel® Cluster Studio XE by using them to build and analyze LAMMPS (http://lammps.sandia.gov/), a complex cluster application and benchmark used in Spec MPI*. |                                                          |

| Checklist for Programming Intel® Xeon Phi™ Coprocessors,                                                                                                                                  |                                                          |

| BY JAMES REINDERS.                                                                                                                                                                        | 22                                                       |

| Offers key tips for programming a high degree of parallelism, while using familiar programming methods and the latest Intel® tools supporting the Intel® Xeon Phi™ coprocessor.           |                                                          |

| Advanced Vectorization, BY GEORG ZITZLSBERGER                                                                                                                                             | 28                                                       |

| Applying some of the vectorization techniques enabled by Intel compilers and their Intel® Cilk™ Plus technologies to an example application.                                              |                                                          |

| Optimizing Correlation Analysis of Financial Market Data<br>Streams Using Intel® Math Kernel Library,                                                                                     |                                                          |

| BY ZHANG ZHANG, ANDREY NIKOLAEV, AND VICTORIYA KARDAKOVA                                                                                                                                  | 40                                                       |

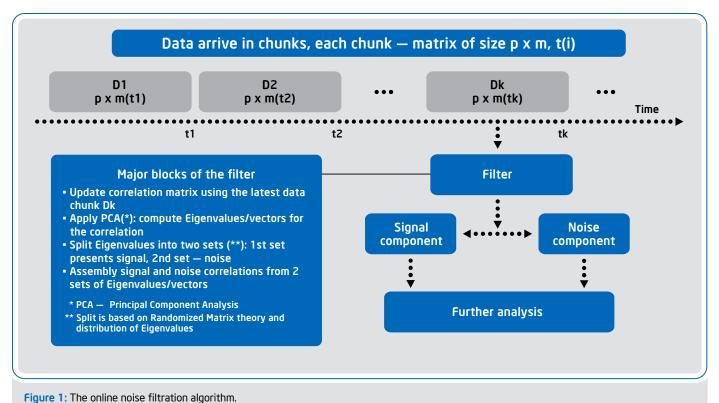

| Demonstrates the performance advantages of Intel® Math Kernel Library in the implementation of the online noise filtration algorithm on a correlation analysis of financial market data.  |                                                          |

### Sign up for future issues | Share with a friend

The Parallel Universe is a free quarterly magazine. Click here to sign up for future issue alerts and to share the magazine with friends.

James Reinders Director of Parallel Programming Evangelism at Intel Corporation. James is a co-author of a new book, Structured Parallel Programming, from Morgan Kaufmann, 2012. His other books include Intel\* Threading Building Blocks: Outfitting C++ for Multicore Processor Parallelism, available in English, Japanese, Chinese, and Korean.

Complexity is every day in high performance and cluster applications. Applications are utilized to solve the increasingly complex problems that we pose. Parallelism is the natural vocabulary for developers trying to ensure that large data stores and demanding workloads run fast, run flawlessly, and helps us get the results we seek.

The conjunction of Intel® Cluster Studio XE 2013 and the Intel® Xeon Phi™ coprocessor makes this an ideal time to explore some of our more interesting development challenges.

We start by seeing Intel Cluster Studio XE 2013 in action in *Using Intel® Software Development Tools to Analyze the Performance of LAMMPS*—as we use new features of this advanced toolset to build and analyze LAMMPS, one of the Spec MPI\* benchmarks.

Next, in Checklist for Programming Intel® Xeon Phi™ Coprocessors, we offer programming tips for applications running on and taking advantage of the capabilities of Intel® Xeon Phi™ coprocessors. Scaling, vector usage, and memory usage can all be improved, and these benefits are preserved when the applications run on Intel® Xeon® processors.

Advanced Vectorization uses an example application to present practical, proven techniques enabled by Intel compilers and their Intel $^{\circ}$  Cilk $^{\circ}$  Plus technologies.

And finally, Optimizing Correlation Analysis of Financial Market Data Streams Using Intel® Math Kernel Library, is at once a case study of extreme complexity—applying an online noise filtration algorithm to correlation analysis in the finance industry—and a proof of the performance gains possible with Intel® Math Kernel Library.

We all live in an increasingly complexity environment—and I hope you are inspired by seeing some ways others are tackling their complex challenges.

James Reinders November 2012

# Using ntel<sup>®</sup> Software Development Tools to Analyze the Performance of

by Walter Shands, Software Development Engineer, Intel

### Introduction

This article highlights the features of Intel® Cluster Studio XE by using them to build and analyze LAMMPS (http://lammps.sandia.gov/), a benchmark used in Spec MPI. We will describe build settings for the Intel® C++ Compiler that optimize performance and how to use the Intel® MPI message library to deliver best-in-class performance for LAMMPS on Intel® architecture-based clusters. We will use Intel® Trace Analyzer and Intel® Trace Collector to illuminate the use of MPI APIs that cause performance problems in LAMMPS, and show how to compare trace files with the Intel Trace Analyzer GUI to get detailed analysis of message passing with aligned timelines. We will also show how to use the Intel® MPI correctness checking library to look for MPI coding errors. Additionally, we will show how to use Intel® VTune™ Amplifier XE to visualize application scaling on individual nodes.

The techniques described in this article may be applied to similar types of complex cluster applications by using diverse technology such as MPI and OpenMP\* across multiple machines.

Our objective is to build LAMMPS, analyze the application with respect to MPI API performance and scaling on individual nodes, and make it run faster. In general, we will want to make sure we use an optimizing compiler like the Intel® C++ Compiler, that compiler settings are optimized for the architecture the application will run on, and that we are using an optimized MPI implementation like Intel MPI. In addition, we want to make sure MPI API call time is a reasonably small percentage of total computation time, and that individual MPI API calls are independent across ranks so MPI call time is minimized. We will also want to ensure that the application running on each node scales to take advantage of all of the CPU cores, so that we use CPU resources efficiently. Intel Cluster Studio XE 2013 provides the tools to build faster MPI applications and analyze MPI application performance.

According to LAMMPS documentation, "LAMMPS is a classical molecular dynamics code that models an ensemble of particles in a liquid, solid, or gaseous state. It can model atomic, polymeric, biological, metallic, granular, and coarse-grained systems using a variety of force fields and boundary conditions."

### Building LAMMPS with the Intel C++ Compiler and Intel MPI Library

To build LAMMPS we created a custom make file by copying one of the provided make files and editing the contents so the LAMMPS build used the Intel C++ Compiler and the Intel MPI Library. Here are some of the settings (Fig. 1):

mpiicpc is the Intel-specific command for building an application using the Intel C++ Compiler and the Intel MPI Library. The MPI Library focuses on making applications perform better on IA-based clusters by implementing the high-performance MPI-2 specification on multiple fabrics. It enables you to quickly deliver maximum end-user performance, even if you change or upgrade to new interconnects, without requiring major changes to the software or operating environment.

To analyze MPI message traffic in an application with Intel Trace Analyzer, we need to collect data into trace files. Intel Trace Collector for MPI applications produces trace files that can be analyzed with the Intel Trace Analyzer performance analysis tool. It records all calls to the MPI library and all transmitted messages, and allows arbitrary user-defined events to be recorded. Instrumentation can be switched on or off at runtime, and a powerful filtering mechanism helps to limit the amount of the generated trace data.

Intel Trace Collector is an add-on for existing MPI implementations; using it merely requires relinking the application with the Intel Trace Collector profiling library. This will enable the tracing of all calls to MPI routines, as well as all explicit message passing. On some platforms, calls to user-level subroutines and functions will also be recorded.

We can use a fully optimized build and capture a trace that will allow us to drill down to source code with Intel Trace Analyzer. The same is true of Intel VTune Amplifier XE, so we use full optimizations in the compiler with the **—03** switch. We want to use the most advanced instruction set for our target nodes, which in our case supports SSE4.2, so we include the **—**SSE4.2 switch since the default for the compiler is SSE2.

We need symbol information to drill down to source code with Intel VTune Amplifier XE and Intel Trace Analyzer, so we include the —g switch. A new feature in Intel VTune Amplifier XE 2013 is that it allows us to drill down to source code even if functions are inlined, so we don't need to include the –fno-inline-functions switch as was required for previous versions. Intel Trace Collector requires normal stack frames but the Intel® compiler does not use normal stack frames by default if optimization is enabled, so we must use -fno-omit-frame-pointer to enable the use of normal stack frames.

```

# compiler/linker settings

# specify flags and libraries needed for your compiler

CC =

-g -O3 -xSSE4.2 -fno-alias -fno-omit-frame-pointer -vec-report5 -opt-report3

CCFLAGS =

-opt-report-phase=all

DEPFLAGS =

LINK =

mpiicpc

LINKFLAGS =

-lstdc++ -lpthread -liomp5

LIB =

ARCHIVE =

ar

ARFLAGS =

-rc

SIZE =

size

Figure 1

```

### Running a LAMMPS Benchmark

LAMMPS runs by reading commands from stdin, and you can write an input script of commands to set up and simulate particle dynamics. There is a set of input scripts for tests and benchmarks provided in the LAMMPs distribution. We used the script for a standard Lennard-Jones benchmark.

This is an example of running LAMMPS with a Lennard-Jones benchmark script (Fig. 2):

mpirun is the command used to launch an MPI job. Here it runs the LAMMPS application on the nodes listed in the cluster.hosts file; in this case my build is called "Imp\_walt". The —trace switch causes Intel Trace Collector to profile the LAMMPS application by preloading the Intel Trace Collector library, and the environment variable VT\_PCTRACE sets the call stack depth.

The —bootstrap slurm option selects a built-in bootstrap server to use, which is the basic remote node access mechanism provided on the nodes, and —n 8 says to use eight processes in the run. The —perhost 1 option is important: it says to create 1 MPI process on each node in a round-robin fashion. Without it, an MPI process is started for every core available on the first node. For example, if the nodes each have 12 cores and we use the —n 8 option, but not the —perhost option (or equivalently the —rr option), then eight MPI processes would be started on one node.

The —var x 2 —var y 2 —var z 2 LAMMPS flags are for scaling the problem 2x in each x, y, and z direction, where the data to work on is arrayed as a grid of x \* y \* z 3d subdomains. We set the variables to two so that there is a 3D subdomain assigned to each of the eight processors used.

We created eight MPI processes to run in total, each on a separate node for our first run of the Lennard-Jones benchmark, and analyzed the trace with Intel Trace Analyzer.

### **Analyzing MPI Communications**

When you develop MPI applications it is important to look at how much time the MPI calls are consuming compared to application time and the load balance for each MPI call. Intel Trace Analyzer provides this data through various charts and profiles.

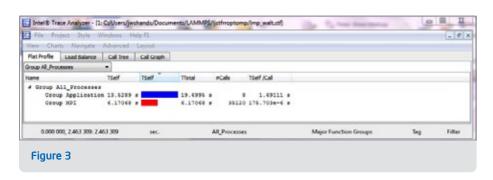

### The Flat Profile

The Flat Profile view tells us how much time user code took and can tell us how much time each MPI API took during the application run. It shows that the total amount of time taken by MPI calls over the whole run of the program is fairly significant compared to application time (**Fig. 3**), and we can use Intel Trace Analyzer to see more details.

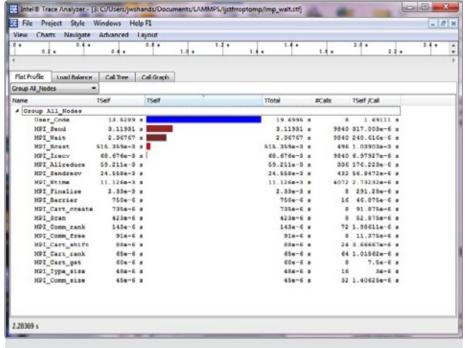

Ungrouping MPI reveals that the MPL\_Send and MPL\_Wait calls are the most expensive in terms of time (Fig. 4).

### The Load Balance Chart

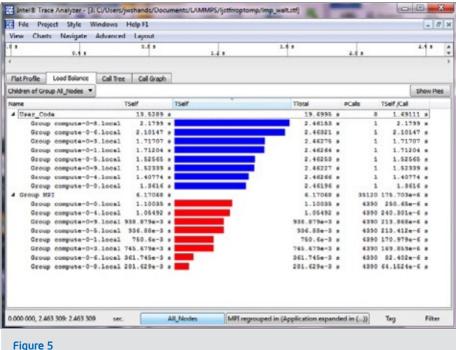

In addition, MPI API call time and application time are not well balanced across nodes, as shown in the Load Balance chart (**Fig. 5**).

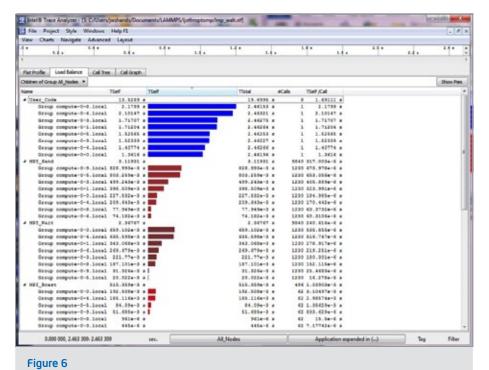

If we look at the MPI function time in finer detail, there are varying times for individual MPI calls across the compute nodes, with most of the time taken on the 0, 4, 5, and 9 compute nodes. This can be an indication of message dependencies that result in reduced application performance (Fig. 6). The Event Chart provides information on whether MPI API calls are interdependent.

Figure 4

rigule 3

#### The Event Chart

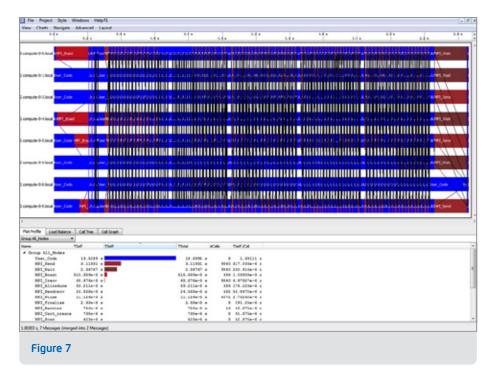

If we open the Event Chart from the Chart menu, it shows us a timeline and horizontal bars with segments representing application code and MPI messages. This gives us an idea of which message APIs were called at a particular time and how long they took to complete. (Fig. 7)

LAMMPS documentation states "For computational efficiency, LAMMPS uses neighbor lists to keep track of nearby particles ... On parallel machines, LAMMPS uses spatial-decomposition techniques to partition the simulation domain into small 3D subdomains, one of which is assigned to each processor. Processors communicate and store "ghost" atom information for atoms that border their sub-domain .... The Comm class performs interprocessor communication, typically of ghost atom information. This usually involves MPI message exchanges with six neighboring processors in the 3D logical grid of processors mapped to the simulation box."

Our input script called for 100 time steps with neighbor lists of particles rebuilt after 20 time steps. The communication of atom information occurs at each time step, and the Event Chart allows us to see the communication graphically. We can see the five groups of 20 atom information exchanges show up as black lines.

#### THE PARALLEL UNIVERSE

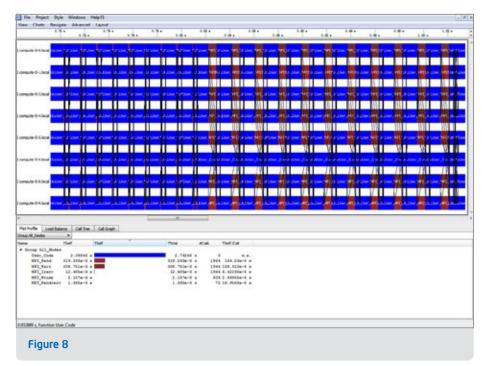

If we zoom into the event chart, we can get details on the message passing calls. Here is the zoom into one of the five groups (Fig. 8).

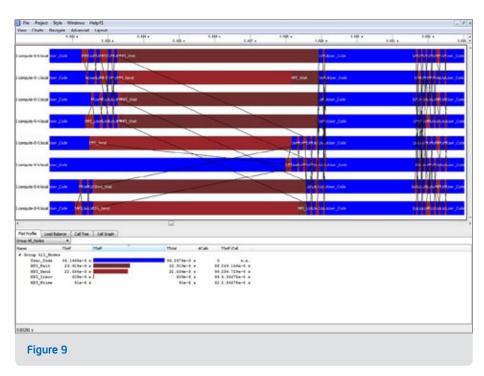

A further zoom into an atom information exchange provides a look at the individual MPI API calls over time. The black lines indicate which ranks or processes exchanged messages, and there are two distinct time periods within a time step where messages are exchanged (Fig. 9). The messages between ranks look fairly independent, since we do not see a stair-step pattern, which is indicative of message interdependence—although some of the MPI APIs in the first message exchange sequence take quite a bit longer to complete than the same MIP APIs in the second message exchange sequence during this application time step.

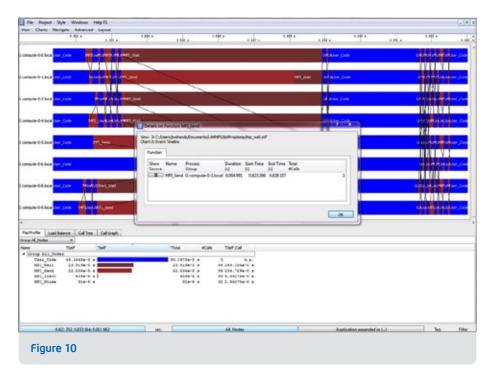

If we want to get information on a message or MPI API call, we can simply right-click on a black message line or on the MPI call segment to bring up the message details dialog (Fig. 10).

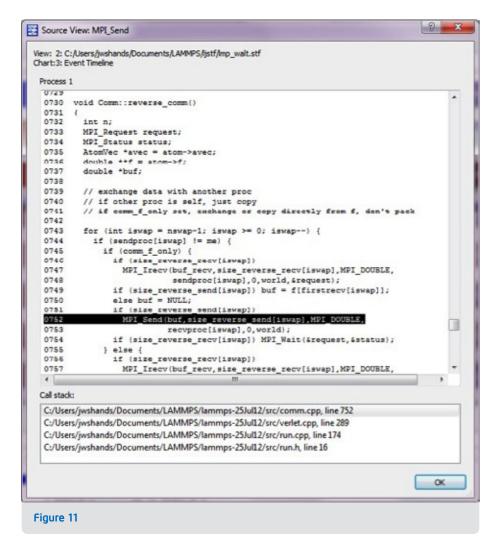

If we want to look at the source code where the MPI call originated and we have debug symbols, we can click on the Show Source button in the dialog box to display the location of the MPI call and the call stack (Fig. 11). In our case, this confirms that in the first message exchange sequence the Comm class is calling reverse\_comm to exchange ghost atom information or, more specifically, forces on ghost atoms are communicated and summed back to their corresponding owned atoms.

The same source code analysis confirms that the second message exchange sequence is where the Comm class calls forward\_comm to distribute coordinates of ghost atoms to each process. This is done at each time step (Fig. 12).

### The Qualitative Timeline

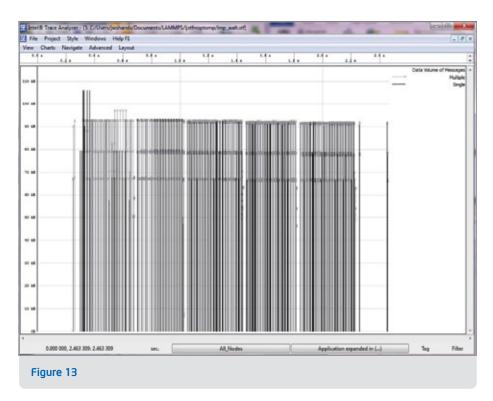

Another metric we may want to examine is the data volume that is being transmitted with each message over time. To see this, we use the Qualitative Timeline, selected from the Chart menu, and right-click on the window to select Messages and Data Volume from the pop-up menu as the items to display (Fig. 13).

The data volume per message is fairly consistent over time—with a maximum at about 93 KB. Additionally, we can see the duration and transfer rate by picking those attributes for the display.

```

Source View: MPI_Send

View: 2: Compare C:/Users/jwshands/Documents/LAMMPS/ljstfrroptomp/lmp_walt.stf (A) with C:/Users/jwshands/Documents/LAMMPS/ljstfrroptomp/lmp_walt.stf (B) Chart: 1: Event Timeline

Group compute-0-5.local

0659

0660

0661

void Comm::forward_comm(int dummy)

0662

0663

int n:

MPI Request request;

0664

MPI_Seasus seasus;

0666

AtomVec *avec = atom->avec;

double **x = atom->x;

0667

double *buf;

0668

0669

// exchange data with another proc

0671

// if other proc is self, just copy

0672

// if comm_x_only set, exchange or copy directly to x, don't unpack

0673

0674

for (int iswap = 0; iswap < nswap; iswap++) {

0675

if (sendproc(iswap) != me) {

0676

if (comm_x_only) {

0677

if (size_forward_recv(iswap)) buf = x[firstrecv(iswap)];

0678

else buf = NULL;

if (size_forward_recv[iswap])

0679

MPI_Irecv(buf, size_forward_recv[iswap], MPI_DOUBLE,

0680

recvproc(iswap), 0, world, &request);

0681

0682

n = avec->pack_comm(sendnum[isvap], sendlist[isvap],

buf send,pbc flag(iswap),pbc(iswap));

if (n) MPI Send(buf send,n,MPI DOUBLE,sendproc(iswap),0,world);

0683

0684

MPI_Wait(&request,&status)

(size_forward_recv[iswap])

0686

} else if (ghost_velocity) {

0687

if (size forward recv[iswap])

Call stade

C:/Users/jwshands/Documents/LAMMPS/lammps-25Jul12/src/comm.cpp, line 684

C:/Users/jwshands/Documents/LAMMPS/lammps-25Jul12/src/verlet.cpp, line 239

C:/Users/jwshands/Documents/LAMMPS/lammps-25Jul12/src/run.cpp, line 174

C:/Users/jwshands/Documents/LAMMPS/lammps-25Jul12/src/run.h, line 16

OK

Figure 12

```

Figure 14

### The Quantitative Timeline

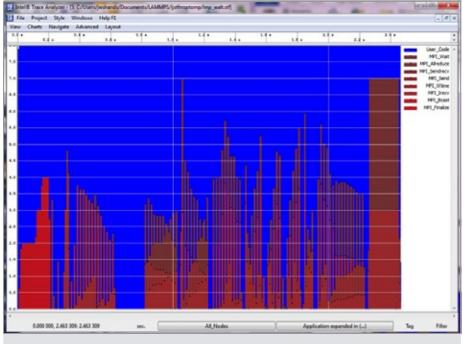

The Quantitative Timeline gives an overview of the parallel behavior of the application. It shows over time how many processes or threads are involved in which function. Along the time axis, the different functions are presented as vertically stacked color bars. The height of these bars is proportional to the number of processes that are currently within the respective function (Fig. 14).

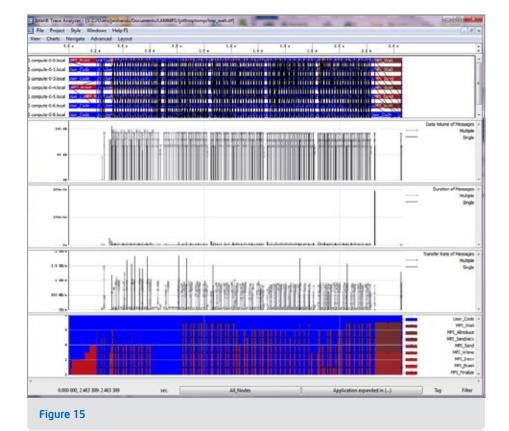

There is also the option to view all of these profiles and charts in a single window working on a common timeline, so patterns and relationships in the data are easier to see (Fig. 15).

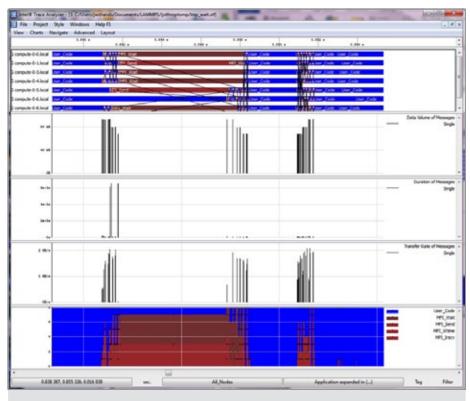

We can also couple the mouse zoom and navigation keys for all of the displayed charts, so zooming in by highlighting a section of the timeline provides a detailed view of the data described above over the same time interval (Fig. 16).

### The Message Profile Chart

To get another view on messages we can use the Message Profile Chart, which categorizes messages by groupings in a matrix and shows the value of several attributes in each cell. By default, the matrix is square with the sending processes as row labels and the receiving processes as column labels. It shows in cell (i, j) the total time spent in transferring messages from sender i to receiver j. This chart also includes per row and per column statistics, which give the sum, the average, and the standard deviation for the respective row or column (Fig. 17).

The chart shows that the most timeconsuming messages originated with compute nodes 0, 1, 3, and 4 sending messages to compute nodes 5, 6, 8, and 9 respectively, while messages sent in the opposite direction are not a performance problem.

### MPI Message Correctness Checking

During development of an MPI application you will need to check for errors. You can do this with the correctness checking feature in Intel Trace Collector by replacing the mpirun command – trace switch with – check. This will not generate a trace file, but will report errors to stdout. Errors include MPI local memory errors, message data type mismatches, message corruption, pending messages, deadlocks, invalid parameters, and others.

Figure 16

Here is an example of how the correctness checking feature was used to check LAMMPS and reported no errors: **(Fig. 18)**:

```

~/LAMMPS/lammps-25Jul12/bench]> mpirun -f ~/cluster.hosts -check -perhost 1 -bootstrap slurm -n 8 ~/LAMMPS/lammps-25Jul12/src/lmp_walt -var x 2 -var y 2 -var z 2 < in.lj

Figure 18

```

### Application Scaling and Performance Profiling with Intel VTune Amplifier XE

It is important to balance the scalability of each MPI process with the number of MPI processes started on each node. For example, if we have an MPI application that scales to 12 cores and have 12 cores on each node, then we can start one MPI process per node and utilize all the CPUs effectively.

To check this on LAMMPS, we run Intel VTune Amplifier XE 2013 and a single LAMMPS process on each node. This allows us to collect performance data on each MPI process to see how well LAMMPS utilizes all of the cores on the node. Here is the command line to collect hotspot data for the LAMMPS process on each node using Intel VTune Amplifier XE (Fig. 19).

```

~/LAMMPS/lammps-25Jul12/bench]> mpirun -f ~/cluster.hosts -perhost 1 -bootstrap slurm -n 8 amplxe-cl -collect hotspots ~/LAMMPS/lammps-25Jul12/src/lmp_o3 -var x 2 -var y 2 -var z 2 < in.lj Figure 19

```

Essentially, we are using the mpirun command to run Intel VTune Amplifier XE, which in turn launches an instance of LAMMPS. Intel VTune Amplifier XE will run on each node and collect data for the LAMMPS process. The results data is stored in separate folders for each node on the machine where the mpirun command was executed.

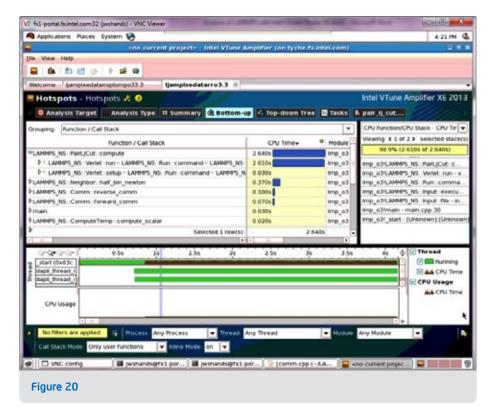

Intel VTune Amplifier XE results tell us that the application is using only one thread for computation, and that most of the run time is concentrated in a function called PairLJCut::compute in file pair\_lj\_cut.cpp. (Fig. 20)

The runtime was about 3.15 seconds in default mode (Fig. 21).

```

mpirun -f ~/cluster.hosts -perhost 1 -bootstrap slurm -n 8 ~/LAMMPS lammps-

25Jul12/src/lmp_o3 -var x 2 -var y 2 -var z 2 < in.lj

LAMMPS (25 Jul 2012)

using 24 OpenMP thread(s) per MPI task

Lattice spacing in x,y,z = 1.6796 1.6796

Created orthogonal box = (0 0 0) to (67.1838 67.1838 67.1838)

2 by 2 MPI processor grid

Created 256000 atoms

Setting up run . . .

Memory usage per processor = 55.2672 Mbytes

Step Temp E_pair E_mol TotEng Press

0    1.44   -6.7733681    0   -4.6133765   -5.019674

100    0.75865617   -5.7603259    0   -4.6223461    0.19586104

Loop time of 3.14944 on 192 procs (8 MPI x 24 OpenMP) for 100 steps with 256000 atoms</pre>

Figure 21

```

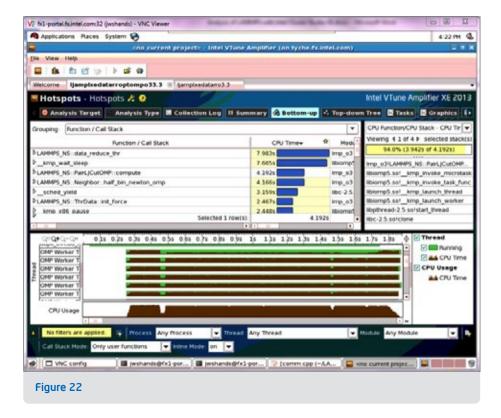

Next, we want to include threading by using an optimization package provided in the LAMMPS distribution to see if performance improves. The amount of scaling we get will determine how many processes we will start on each node to get optimal use of the computational resources. We include an optimization package that provides threading via OpenMP called USER-OMP. Intel VTune Amplifier XE shows multiple threads of execution with significant CPU activity (Fig.22).

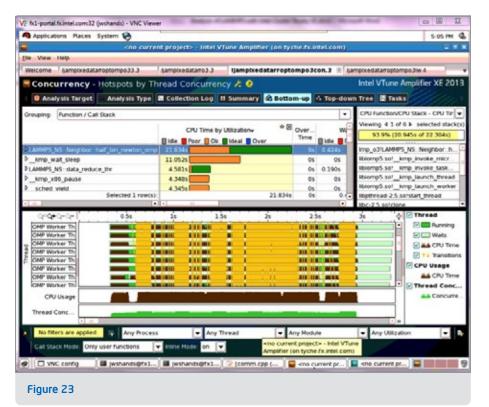

Intel VTune Amplifier XE Thread Concurrency data shows that the application threads are consuming significant CPU time over the time of the run (Fig. 23).

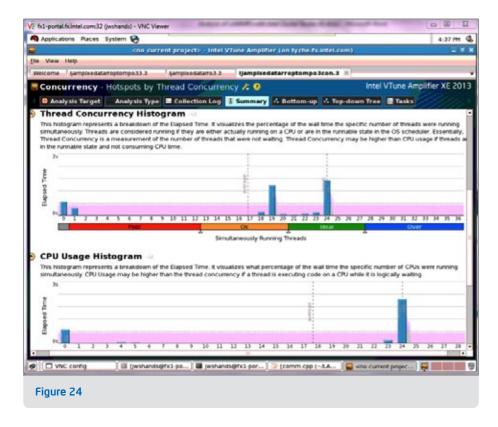

The histograms below **(Fig. 24)** show threads and CPUs are running simultaneously most of the time, indicating the application is utilizing computational resources effectively.

The runtime was about 1.20 seconds with the optimization package, much less than without the package, even though there was a significant amount of OpenMP wait time introduced (Fig. 25).

```

> mpirun -f ~/cluster.hosts -perhost 1 -bootstrap slurm -n 8 ~/LAMMPS/lammps-

25Jul12/src/lmp o3 -sf omp -var x 2 -var y 2 -var z 2 < in.lj

LAMMPS (25 Jul 2012)

using 24 OpenMP thread(s) per MPI task

Lattice spacing in x,y,z = 1.6796 \ 1.6796 \ 1.6796

Created orthogonal box = (0 \ 0 \ 0) to (67.1838 \ 67.1838 \ 67.1838)

2 by 2 by 2 MPI processor grid

Created 256000 atoms

Last active /omp style is pair style lj/cut/omp

Setting up run ...

Memory usage per processor = 59.4847 Mbytes

Step Temp E pair E mol TotEng Press

0 1.44 -6.7733681 0 -4.6133765 -5.019674

100 0.75865617 -5.7603259 0 -4.6223461 0.19586104

Loop time of 1.19531 on 192 procs (8 MPI x 24 OpenMP) for 100 steps with 256000 atoms

Figure 25

```

### Memory and Threading Error Checking of MPI Processes with Intel® Inspector XE

We can also use Intel® Inspector XE to check for threading errors or memory errors in an MPI application. Here is the command line we used to check for memory errors and to pinpoint their location (Fig. 26).

Data results are collected and stored for each node in a manner similar to Intel VTune Amplifier XE. We can open the results in the Intel Inspector XE GUI just as we did for Intel VTune Amplifier XE results.

### Support of Manycore Architectures: Intel® Xeon Phi™ Coprocessors

One of the newest additions to high performance computing is the Intel® Xeon Phi™ coprocessor, which is designed to provide efficient performance for highly parallel applications. Common programming models for Intel® Xeon processors extend to Intel Xeon Phi coprocessors—so as developers embrace high degrees of parallelism, they don't need to rethink the entire problem.

The practical result of this, in our case, is that it is very easy to run the LAMMPS application on an Intel Xeon Phi coprocessor. All we have to do if we are using the Intel C/C++ Compiler is to rebuild LAMMPS with the –mmic switch for both the compiler and linker. Here is the relevant part of the makefile (Fig. 27):

```

# compiler/linker settings

# specify flags and libraries needed for your compiler

CC = mpiicpc

CCFLAGS = -mmic -g -03 -openmp -fno-alias-fno-omit-frame-pointer

DEPFLAGS = -M

LINK = mpiicpc

LINKFLAGS = -mmic

LIB = -lstdc++ -lpthread -liomp5

...

Figure 27

```

You will also need to have libiomp5.so and libVT.so on the coprocessor to use OpenMP and Intel Trace Collector. There are a couple of choices on where to run the application. To run four LAMMPS processes on the host and eight LAMMPS processes on the Intel Xeon Phi coprocessor, use a command similar to the following. We use our original LAMMPS build for the host and the one built with the –mmic switch on the Intel Xeon Phi coprocessor (Fig. 28).

To run all eight LAMMPS processes on the Intel Xeon Phi coprocessor, use the following command line indicating the working directory on the coprocessor (Fig. 29):

```

$ mpiexec -wdir ~/. -host mic0 -n 8 ~/lmp_mic -sf omp -var x 2 -var y 2 -var z 2 < in.lj

Figure 29</pre>

```

In addition, we can still use Intel Trace Collector to get MPI information from applications running on Intel Xeon Phi coprocessors, and the command line switch is the same (Fig. 30).

```

$ mpiexec -trace -host sc-mic -n 4 ../src/lmp_o3 -sf omp -var x 2 -var y 2 -var z 2 < in.lj : -wdir ~/.

-host mic0 -n 8 ~/lmp_mic -sf omp -var x 2 -var y 2 -var z 2 < in.lj</pre>

Figure 30

```

Or, to run and collect traces only on the Intel Xeon Phi coprocessor (Fig. 31):

```

$ mpiexec -trace -wdir ~/. -host mic0 -n 8 ~/lmp_mic -sf omp -var x 2 -var y 2 -var z 2 < in.lj

Figure 31</pre>

```

### Conclusion

Intel Trace Collector and Intel Trace Analyzer give us insight into MPI application information like message timing, load balancing, and data volume so we can more easily optimize MPI applications. In the case of LAMMPS, we could see the most time-consuming APIs and where they were called.

Intel VTune Amplifier XE provides CPU utilization and hotspot information for each MPI process, which is vital to ensuring those processes scale on each node. Intel VTune Amplifier XE showed us that the USER-OMP package for LAMMPS provided significant CPU resource utilization on a node, allowing the application to scale well on a two-socket 12-core node.

Intel Inspector XE and the check feature of Intel MPI help find MPI, memory, and threading errors in our application, and the Intel C++ Compiler and Intel MPI provide highly optimized binaries and MPI infrastructure that results in a high performance application.

This is only a glimpse into the power of Intel® Software Development tools to create and analyze complex software applications using diverse technology such as MPI and OpenMP across multiple machines. For more information on Intel Software Development tools see <a href="https://www.intel.com/software/products">www.intel.com/software/products</a>.  $\square$

**CHECKLIST FOR PROGRAMMING -**

# Intel® Xeon Phi Coprocessors

by James Reinders,

Director, Software Evangelist, Intel

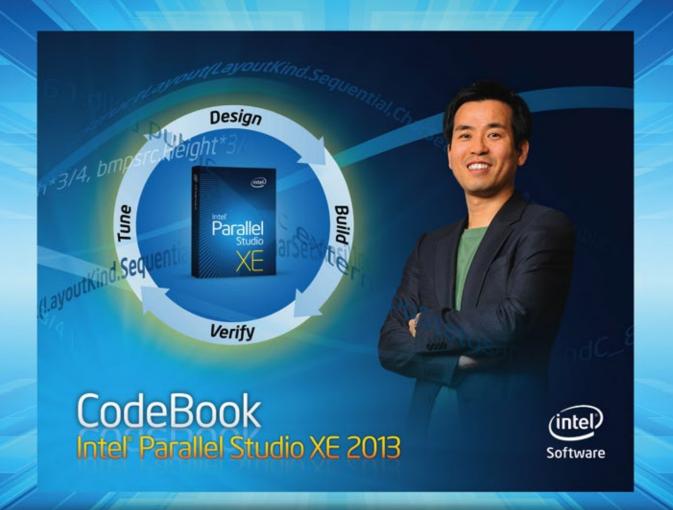

The Intel® Xeon Phi™ coprocessor extends the reach of the Intel® Xeon® family of computing products into higher realms of parallelism. This article offers the key tips for programming such a high degree of parallelism, while using familiar programming methods and the latest Intel® Parallel Studio XE 2013 and Intel® Cluster Studio XE 2013—which both support the Intel Xeon Phi coprocessor.

### Checklist

### A checklist for programming for an Intel Xeon Phi coprocessor looks like this:

- Make sure your application scales beyond 100 threads (usually 150 or more).

- Make sure your application either:

- Does most computations as efficient vector instructions (requires vectorization)

- Uses a lot of memory bandwidth with decent locality of reference

- The application is written using your favorite programming languages and parallel models to achieve the above.

- Use your favorite tools, the same ones you use for programming for Intel® Xeon® processors. Get the latest versions that include support for Intel® Xeon Phi™ coprocessor support (such as Intel® Cluster Studio XE 2013, Intel® Parallel Studio XE 2013, Rogue Wave TotalView\* debugger and IMSL\* Library, NAG Library\*, or Allinea DDT\* debugger)

It is worth explaining this checklist in more depth, and that is the purpose of this article. You can see that preparing for Intel Xeon Phi coprocessors is primarily about preparing for a 50+ core x86 SMP system with 512-bit SIMD capabilities. That work can happen on most any large, general purpose system, especially one based on Intel Xeon processors. Intel Parallel Studio XE 2013 and Intel Cluster Studio XE 2013 will support your work on an Intel Xeon processor-based system with or without Intel Xeon Phi coprocessors. All the tools you need are in one suite.

### Introduction

Intel Xeon Phi coprocessors are designed to extend the reach of applications that have demonstrated the ability to reach the scaling limits of Intel Xeon processor-based systems, and have also maximized usage of available vector capabilities or memory bandwidth. For such applications, the Intel Xeon Phi coprocessors offer additional power-efficient scaling, vector support, and local memory bandwidth, while maintaining the programmability and support associated with Intel Xeon processors.

Advice for successful programming can be summarized as: "Program with lots of threads that use vectors with your preferred programming languages and parallelism models." Since most applications have not yet been structured to take advantage of the full magnitude of parallelism available in an Intel Xeon Phi coprocessor, understanding how to restructure to expose more parallelism is critically important to enable the best performance. This restructuring itself will generally yield benefits on most general purpose computing systems—a bonus due to the emphasis on common programming languages, models, and tools across the Intel Xeon family of products. You may refer to this bonus as the dual-transforming-tuning advantage.

A system that includes Intel Xeon Phi coprocessors will consist of one or more nodes (a single node computer is "just a regular computer"). A typical node consists of one or two Intel Xeon processors, plus one to eight Intel Xeon Phi coprocessors. Nodes cannot consist of only coprocessors.

### The First Intel Xeon Phi Coprocessor, Codename Knights Corner

While programming does not require deep knowledge of the implementation of the device, it is definitely useful to know some attributes of the coprocessor. From a programming standpoint, treating it as an x86-based SMP-on-a-chip with over 50 cores, over 200 hardware threads, and 512-bit SIMD instructions is the key.

The cores are in-order, dual-issue x86 processor cores (which trace some history to the original Intel® Pentium® design). But with the addition of 64-bit support, four hardware threads per core, power management, ring interconnect support, 512 bit SIMD capabilities, and other enhancements, these are hardly the Intel Pentium cores of 20 years ago. The x86-specific logic (excluding L2 caches) makes up less than 2 percent of the die for an Intel Xeon Phi coprocessor.

Here are key facts about the first Intel Xeon Phi coprocessor product:

- It is a coprocessor (requires at least one processor in the system); in production in 2012

- Boots and runs Linux\* (source code available at http://intel.com/software/mic)

- It is supported by standard tools including Intel Parallel Studio XE 2013.

Listings of additional tools available can be found online (http://intel.com/software/mic).

- > It has many cores:

- More than 50 cores (This will vary within a generation of products, and between generations. It is good advice to not hard code applications to a particular number.)

- In-order cores support 64-bit x86 instructions with uniquely wide SIMD capabilities.

- Four hardware threads on each core (resulting in more than 200 hardware threads on a single device) are primarily used to hide latencies implicit in an in-order microarchitecture. As such, these hardware threads are much more important for HPC applications to utilize than hyperthreads on an Intel Xeon processor.

- Cache coherent across the entire coprocessor.

- Each core has a 512K L2 cache locally with high-speed access to all other L2 caches (making the collective L2 cache size over 25M).

- > Special instructions in addition to 64-bit x86:

- Uniquely wide SIMD capability via 512-bit wide vectors instead of MMX, SSE or AVX.

- High performance support for reciprocal, square root, power, and exponent operations

- Scatter/gather and streaming store capabilities for better effective memory bandwidth

- Performance monitoring capabilities for tools like Intel® VTune™ Amplifier XE 2013

### Maximizing Parallel Program Performance

The choice whether to run an application solely on Intel Xeon processors, or to extend an application run to utilize Intel Xeon Phi coprocessors, will always start with two fundamentals:

- Scaling: Is the scaling of an application ready to utilize the highly parallel capabilities of an Intel Xeon Phi coprocessor? The strongest evidence of this is generally demonstrated scaling on Intel Xeon processors.

- 2. Vectorization and Memory Locality: Is the application either:

- · Making strong use of vector units?

- Able to utilize more local memory bandwidth than available with Intel Xeon processors?

If both of these fundamentals are true for an application, then the highly parallel and power-efficient Intel Xeon Phi coprocessor is most likely worth evaluating.

### Ways to Measure Readiness for Highly Parallel Execution

To know if your application is maximized on an Intel Xeon processorbased system, you should examine how your application scales, as well as how it uses vectors and memory. Assuming you have a working application, you can get some impression of where you are with regards to scaling and vectorization by doing a few simple tests.

To check scaling, create a simple graph of performance as you run with various numbers of threads (from one up to the number of cores, with attention to thread affinity) on an Intel Xeon processor-based system. This can be done with settings for OpenMP\*, Intel® Threading Building Blocks (Intel® TBB) or Intel® Cilk™ Plus (e.g., OMP\_NUM\_THREADS for OpenMP). If the performance graph indicates any significant trailing off of performance, you have tuning work you can do to improve your application before trying an Intel Xeon Phi coprocessor.

To check vectorization, compile your application with and without vectorization. If you are using Intel compilers: disable vectorization via compiler switch: -no-vec, use at least -02 xhost for vectorization. Compare the performance you see. If the performance difference is insufficient, you should examine opportunities to increase vectorization. Look again at the dramatic benefits vectorization may offer as illustrated in Figure 7. If you are using libraries, such as the Intel® Math Kernel Library (Intel® MKL), you should consider that time in Intel MKL routines offer vectorization invariant to the compiler switches. Unless your application is bandwidth limited, effective use of Intel Xeon Phi coprocessors should be done with most cycles executing having computations utilizing the vector instructions. While some may tell you that "most cycles" needs to be over 90 percent, we have found this number to vary widely based on the application and whether the Intel Xeon Phi coprocessor needs to be the top performance source in a node or just to contribute to performance.

The Intel® VTune™ Amplifier XE 2013 can help measure computations on Intel Xeon processors and Intel Xeon Phi coprocessor to assist in your evaluations.

Aside from vectorization, being limited by memory bandwidth on Intel Xeon processors can indicate an opportunity to improve performance with an Intel Xeon Phi coprocessor. In order for this to be most efficient, an application needs to exhibit good locality of reference and utilize caches well in its core computations.

The Intel VTune Amplifier XE product can be utilized to measure various aspect of a program, and among the most critical is "L1 Compute Density." This is greatly expanded upon in a paper titled Using Hardware Events for Tuning on Intel® Xeon Phi™ Coprocessor (codename: Knights Corner).

When using MPI, it is desirable to see a communication vs. computation ratio that is not excessively high in terms of communication. Because programs vary so much, this has not been well characterized other than to say that, like other machines, Intel Xeon Phi coprocessors favor programs with more computation vs. communication. Programs are most effective using a strategy of overlapping communication and I/O by computation. Intel® Trace Analyzer and Collector, part of Intel Cluster Studio XE 2013, is very useful for profiling. It can be used to profile MPI communications to help visualize bottlenecks and understand the effectiveness of overlapping with computation to characterize your program.

### Compiler and Programming Models

No popular programming language was designed for parallelism. In many ways, Fortran has done the best job adding new features, such as DO CONCURRENT, to address parallel programming needs, as well as benefiting from OpenMP. C users have OpenMP, as well as Intel Cilk Plus. C++ users have embraced Intel Threading Building Blocks and, more recently, have Intel Cilk Plus to utilize as well. C++ users can use OpenMP as well.

Figure 1: The double advantage of transforming-and-tuning means that optimizations are shared across the Intel®Xeon® family of products, Capabilities of Intel Xeon processors are extended by Intel® Xeon Phi™ coprocessors.

Intel Xeon Phi coprocessors offer the full capability to use the same tools, programming languages, and programming models as an Intel Xeon processor. However, with this coprocessor designed for high degrees of parallelism, some models are more interesting than others.

In essence, it is quite simple: an application needs to deal with having lots of tasks (call them "workers" or "threads" if you prefer), and deal with vector data efficiently (a.k.a., vectorization).

There are some recommendations we can make based on what has been working well for developers. For Fortran programmers, use OpenMP, DO CONCURRENT, and MPI. For C++ programmers, use Intel TBB, Intel Cilk Plus, and OpenMP. For C programmers, use OpenMP and Intel Cilk Plus. Intel TBB is a C++ template library that offers excellent support for task-oriented load balancing. While Intel TBB does not offer vectorization solutions, it does not interfere with any choice of solution for vectorization. Intel TBB is open source and available on a wide variety of platforms supporting most operating systems and processors. Intel Cilk Plus is a bit more complex in that it offers both tasking and vectorization solutions. Fortunately, Intel Cilk Plus fully interoperates with Intel TBB. Intel Cilk Plus offers a simpler set of tasking capabilities than Intel TBB, but uses keywords in the language to enable full compiler support for optimizing.

Intel Cilk Plus also offers elemental functions, array syntax, and "#pragma SIMD" to help with vectorization. The best use of array syntax is implemented along with blocking for caches, which unfortunately means naïve use of constructs such as A[:] = B[:] + C[:]; for large arrays may yield poor performance. The best use of array syntax ensures that the vector length of single statements is short (some small multiple of the native vector length, perhaps only 1X). Finally, and perhaps most important to programmers today, Intel Cilk Plus offers mandatory vectorization pragmas for the compiler called "#pragma SIMD." The intent of "#pragma SIMD" is to do for vectorization what OpenMP has done for parallelization. Intel Cilk Plus requires compiler support. It is currently available from Intel for Windows\*, Linux\*, and Apple OS\* X. It is also available in a branch of qcc.

If you are happy with OpenMP and MPI, you are in great shape to use Intel Xeon Phi coprocessors. Additional options may be interesting to you over time, but OpenMP and MPI are enough to get great results. Your key challenge will remain vectorization. Auto-vectorization may be enough for you, especially if you code in Fortran, with the possible additional considerations for efficient vectorization, such as alignment and unit-stride accesses. The "#pragma SIMD" capability of Intel Cilk Plus (available in Fortran, too) is worth a look. In time, you may find it has become part of OpenMP.

Dealing with tasks means specification of tasks, and load balancing amongst them. MPI has provided this capability for decades with full flexibility and control given to the programmer. Shared memory programmers have Intel TBB and Intel Cilk Plus to assist them. Intel TBB has widespread usage in the C++ community. Intel Cilk Plus extends Intel TBB to offer C programmers a solution, as well as help with vectorization in C and C++ programs.

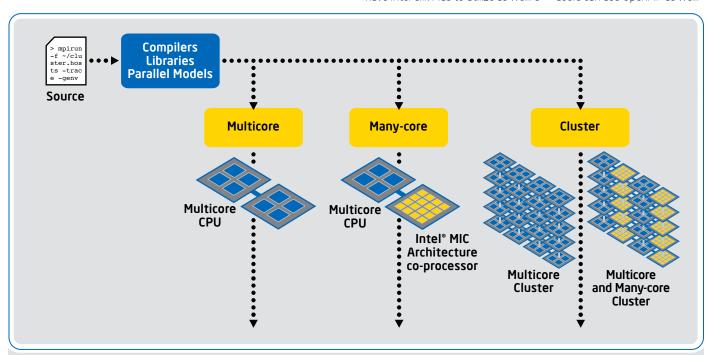

### Coprocessor Major Usage Model: MPI vs. Offload

Given that we know how to program the Intel Xeon processors in the host system, the question arises of how to involve the Intel Xeon Phi coprocessors in an application. There are two major approaches: (1) "offload" selective portions of an application to the Intel Xeon Phi coprocessors, and (2) run an MPI program where MPI ranks can exist on Intel Xeon processors cores, as well as on Intel Xeon Phi coprocessor cores with connections made by MPI communications. The first is call "offload mode" and the second "native mode." The second does not require MPI to be used, because any SMP programming model can be employed, including just running on a single core. There is no machine "mode" in either case, only a programming style that can be intermingled in a single application if desired. Offload is generally used for finer-grained parallelism and, as such, generally involves localized changes to a program. MPI is more often done in a coarse-grained manner, often requiring more scattered changes in a program. RDMA support for MPI is available.

The choice is certain to be one of considerable debate for years to come. Applications that already utilize MPI can actually use either method by either limiting MPI ranks to Intel Xeon processors and use offload to the coprocessors, or distributing MPI ranks across the coprocessors. It is possible that the only real MPI ranks be established on the coprocessor cores, but if this leaves the Intel Xeon processors unutilized then this approach is likely to give up too much performance in the system.

Being separate and on a PCle bus creates two additional issues: (1) the limited memory on the coprocessor card, and (2) the benefits of minimizing communication to and from the card. It is worth noting as well, that the number of MPI ranks used on an Intel Xeon Phi coprocessor should be substantially less than the number of cores—in no small part because of limited memory on the coprocessor. Consistent with parallel programs in general, the advantages of overlapping communication (e.g., MPI messages or offload data movement) with computation are important to consider, as well as techniques to load balance work across all available cores. Of course, involving Intel Xeon processor cores and Intel Xeon Phi coprocessor cores adds the dimension of "big cores" and "little cores" to the balancing work, even though they share x86 instructions and programming models. While MPI programs often already tackle the overlap of communication and computation, the placement of ranks on coprocessor cores still requires dealing with the highly parallel programming needs and limited memory. This is why an offload model can be attractive, even within an MPI program.

The offload model for Intel Xeon Phi coprocessors is quite rich. The syntax and semantics of the Intel® Language Extensions for Offload are generally a superset of other offload models including OpenACC. This provides for greater interoperability with OpenMP; ability to manage multiple coprocessors (cards); and the ability to offload complex program components that an Intel Xeon Phi coprocessor can process, but that a GPU could not (and hence, OpenACC does not allow). We expect that a future version of OpenMP will include offload directives that provide support for these needs, and Intel plans to support such a standard for Intel Xeon Phi coprocessors

as part of our commitment to providing OpenMP capabilities. Intel Language Extensions for Offload also provides for an implicit sharing model that is beyond what OpenMP will support. It rests on a shared memory model supported by Intel Xeon Phi coprocessors that allow a shared memory programming model (Intel calls this "MYO") between Intel Xeon processors and Intel Xeon Phi coprocessors. This is most similar to partitioned global address space (PGAS) programming models; not an extension provided by OpenMP. The Intel "MYO" capability offers a global address space within the node, allowing sharing of virtual addresses for select data between processors and coprocessor on the same node. It is offered in C and C++, but not Fortran, since future support of coarray will be a standard solution to the same basic problem. Offloading is available as Fortran offloading via pragmas, C/C++ offloading with pragmas, and optionally shared (MYO) data. Use of MPI can also distribute applications across the system.

## Summary: Transforming-and-Tuning Double Advantage

Programming should not be called easy, and neither should parallel programming. However, we can work to keep the fundamentals the same: maximizing parallel computations and minimizing data movement. Parallel computations are enabled through scaling (more cores and threads) and vector processing (more data processed at once). Minimal data movement is an algorithmic endeavor, but can be eased through the higher bandwidth between memory and cores that is available with the Intel® Many Integrated Core (Intel® MIC) architecture used by Intel Xeon Phi coprocessors. This leads to parallel programming using the same programming languages and models across the Intel Xeon family of products, which are generally also shared across all general purpose processors in the industry. Languages such Fortran, C, and C++ are fully supported. Popular programming methods such as OpenMP, MPI, and Intel TBB are fully supported. Newer models with widespread support such as Coarray Fortran, Intel Cilk Plus, and OpenCL\* can apply as well.

Tuning on Intel Xeon Phi coprocessors for scaling, and vector and memory usage, also benefits the application when run on Intel Xeon processors. Maintaining a value across the Intel Xeon family is critical, as it helps preserve past and future investments. Applications that initially fail to get maximum performance on Intel Xeon Phi coprocessors generally trace problems back to scaling, vector usage, or memory usage. When these issues are addressed, the improvements to the application usually have a related positive effect when run on Intel Xeon processors. This is the double advantage of "transforming-and-tuning," and developers have found it to be among the most compelling features of the Intel Xeon Phi coprocessors.  $\square$

### Learn More

Additional material regarding programming for Intel Xeon Phi coprocessors can be found at http://intel.com/software/mic.

Parallel Programming Community: http://software.intel.com/en-us/parallel/

Advanced Vector Extensions: http://software.intel.com/en-us/avx/

Intel Guide for Developing Multithreaded Applications: http://software.intel.com/en-us/articles/intel-guide-for-developing-multithreaded-applications/

## ispc: Intel® Xeon® and Intel® Xeon Phi™ support now

JAMES REINDERS, (Intel)

Director of Parallel Programming Evangelism

Vectorization is an industry-wide challenge—and if you are interested in seeing some one of the industry-leading exploration projects (and trying it on your code), then you may want to look at ispc.

ispc is an R&D compiler for a C-based language that is targeted to exploring the performance available from doing SPMD (single program, multiple data) computation on SIMD units found on CPUs and on Intel® Xeon Phi™ coprocessors (using the Intel® Many Integrated Core [MIC] architecture). It has delivered performance competitive with hand-coded SSE and AVX for a variety of graphics and throughput kernels, and typically delivers a 3x to 4x speedup vs. scalar C and C++ code on SSE and a 5 to 7x speedup on AVX (for computations that are amenable to SPMD implementation), while still providing the ease of use of a C-like language.

The paper "ispc: A SPMD Compiler for High-Performance CPU Programming" by Matt Pharr and Bill Marks won Best Paper Award at InPar 2012. It is an excellent paper that articulates the challenges of vectorization and explains the important context very well. It also advances a solid demonstration of what is possible when you think about SPMD on SIMD models clearly...

SEE THE REST OF JAMES' BLOG:

### Visit Go-Parallel.com

Browse other blogs exploring a range of related subjects at Go Parallel: Translating Multicore Power into Application Performance.

# ADVANCED Vectoriz

by Georg ZitzIsberger, Technical Consulting Engineer, Intel

### Issue 10 of the *Parallel Universe Magazine* featured a basic introduction to vectorization.

However, this parallelization technique using Intel® compilers is neither black nor white. There are many variations that impact the degree of vectorization, and the performance of the final application. For large-scale systems like compute clusters, even small improvements are desirable—vector computation as a per-core feature of the processor quickly amplifies through core and node count.

Here, we demonstrate the most important features and best-known methods by applying some of the vectorization techniques enabled by Intel® compilers and their Intel® Cilk™ Plus technologies to an example application implementing an image processing algorithm.

### **Example Application**

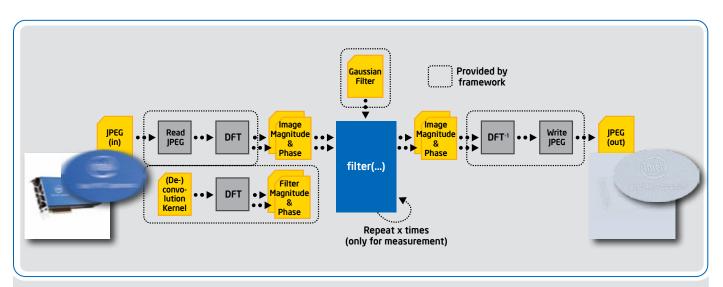

Our example application reads a motion-blurred JPEG image, calling a filter function that undoes the motion blur (i.e., deconvolution) and eliminates low frequencies, before saving it back to a JPEG file. **Figure 1** shows the basic workflow.

To keep the implementation simple, we have decided to implement the filter function in the frequency domain. Thus, before executing the function a forward DFT takes place, transforming the image into two single-precision floating point (32-bit FP) arrays: magnitude and phase. The same is also applied to the (de-)convolution kernel. Initial implementations of the filter function are shown in **Figure 2**, in both C and Fortran versions. After executing the filter function, both output arrays are recombined to an image by inverse DFT and stored as JPEG.

Our example operates on three channel (RGB) images, so magnitude and phase are clustered in the same way. This adds some complexity to the filter regarding the DC values, which does not make it trivial to vectorize (see modulo operation).

The filter is provided as a separate compilation unit. To measure the quality of the vectorization, we record the time it takes to execute it. To lower the noise, the filter is executed multiple times with the same input data. Throughout this article, we only focus on the vectorization of the filter itself. For the detailed implementation and reproducibility you can download the example from our blog.

### Baseline

For our measurements, we are using Ubuntu\* 11.04 (64-bit) running on an Intel® Core™ i7 processor (i7-2600). We're also using 64-bit C/C++ and Fortran compilers shipped with Intel® Composer XE 2013. Since we're working with arrays of single-precision FP values, we also want to make full use of Intel® Advanced Vector Extensions (Intel® AVX), which can process vectors with up to eight such elements at once.

Starting with the baseline implementations for C and Fortran shown in Listing 1, we measure the runtime of repetitive calls to the filter and denote them as baseline. We get those results with standard build options and can see that there's improvement left for vectorization.

Looking at this example, the benefit of vectorization seems quite obvious. But did the baseline already take full advantage of it? A common, though tedious, way to verify this is by analyzing the produced assembly code. For complex algorithms, this easily becomes a challenge and also requires advanced knowledge about the underlying architecture. A better solution would be using Intel® VTune™ Amplifier XE to count executed instructions using SIMD vectors. However, this still requires some knowledge about the architecture. Fortunately there is yet another, much faster, and easier way, that is used here—the Intel compiler vectorization reports (**Table 1**).

First, we start with the C implementation and apply the vectorization report with n=3 to the source file "feature.c." It unveils rather dramatic reasons that turn out to have hindered the compiler from proper vectorization:

Boiling down the redundant output, mostly caused by loop unrolling and permutation of dependencies, reveals that the loop cannot be vectorized because of dependencies between elements of the arrays, including:

- 1. "imgMag"and "imgPhase"

- 2. "imgMag" and "filterMag"

- 3. "imgMag" and "filterPhase"

- 4. "imgMag" and "gaussian"

- 5. "imgPhase" and "filterMag"

- 6. "imgPhase" and "gaussian"

If we list the dependencies this way it turns out that only two arrays, "imgMag" and "imgPhase," are involved. Those are the output parameters from our filter. The report assumes that any write access also influences the other arrays. Why?

Figure 1: Block diagram of the example used. Focus is the implementation of the filter.

```

filter.c:

#include "filter.h"

void filter(

unsigned int size,

float *filterMag, float *filterPhase, // in

float *gaussian)

// in

for(int idx = 0; idx < size; idx++)</pre>

{ // idx%3: RGB values from DC, first 3 elements of "filterMag"

imgMag[idx] /= (filterMag[idx] * 1/filterMag[idx%3] + filterMag[idx%3]);

imgMag[idx] *= gaussian[idx];

imgPhase[idx] -= filterPhase[idx];

filter.f90:

subroutine filter(sze, imgMag, imgPhase, filterMag, filterPhase, gaussian) &

bind(C, name="filter")

use, intrinsic :: ISO_C_BINDING

implicit none

integer(kind=C_INT), VALUE

real(C_FLOAT), dimension(*), intent(inout) :: imgMag

real(C_FLOAT), dimension(*), intent(inout) :: imgPhase

real(C_FLOAT), dimension(*), intent(in) :: filterMag

real(C_FLOAT), dimension(*), intent(in) :: filterPhase

real(C_FLOAT), dimension(*), intent(in)

:: gaussian

integer

:: idx

! mod(idx, 3) + 1: RGB values from DC, first 3 elements of "filterMag"

do idx = 1, sze

imgMag(idx) = imgMag(idx) / (filterMag(idx) *

\frac{1}{\text{filterMag}(\text{mod}(\text{idx}, 3) + 1)} + &

filterMag(mod(idx, 3) + 1));

imgMag(idx) = imgMag(idx) * gaussian(idx)

imgPhase(idx) = imgPhase(idx) - filterPhase(idx)

end do

end subroutine

Figure 2

```

| Syntax                                                                        |                                                                                |                                                                                                                    |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| Linux* and Mac OS* X: -vec-report[n] Windows*: /Qvec-report[n]                |                                                                                |                                                                                                                    |  |  |  |

| Arguments                                                                     |                                                                                |                                                                                                                    |  |  |  |

| n                                                                             | Is a value denoting which diagnostic messages to report.  Possible values are: |                                                                                                                    |  |  |  |

|                                                                               | 0                                                                              | Tells the vectorizer to report no diagnostic information.                                                          |  |  |  |

|                                                                               | 1                                                                              | Tells the vectorizer to report on vectorized loops.                                                                |  |  |  |

|                                                                               | 2                                                                              | Tells the vectorizer to report on vectorized and non-vectorized loops.                                             |  |  |  |

|                                                                               | 3                                                                              | Tells the vectorizer to report on vectorized and non-vectorized loops and any proven or assumed data dependencies. |  |  |  |

|                                                                               | 4                                                                              | Tells the vectorizer to report on non-vectorized loops.                                                            |  |  |  |

|                                                                               | 5                                                                              | Tells the vectorizer to report on non-vectorized loops and the reason why they were not vectorized.                |  |  |  |

| Table 1: Compiler option to turn on the Intel® compiler vectorization reports |                                                                                |                                                                                                                    |  |  |  |

```

filter.c(9): (col. 3) remark: loop was not vectorized: existence of vector dependence.

filter.c(13): (col. 5) remark: vector dependence: assumed FLOW dependence

between imgPhase line 13 and filterMag line 11.

filter.c(11): (col. 5) remark: vector dependence: assumed ANTI dependence

between filterMag line 11 and imgPhase line 13.

filter.c(13): (col. 5) remark: vector dependence: assumed FLOW dependence

between imgPhase line 13 and filterMag line 11.

filter.c(11): (col. 5) remark: vector dependence: assumed ANTI dependence

between filterMag line 11 and imgPhase line 13.

filter.c(13): (col. 5) remark: vector dependence: assumed ANTI dependence

between imgPhase line 13 and imgMag line 11.

filter.c(11): (col. 5) remark: vector dependence: assumed OUTPUT dependence

between imgMag line 11 and imgPhase line 13.

filter.c(13): (col. 5) remark: vector dependence: assumed OUTPUT dependence

between imgPhase line 13 and imgMag line 11.

Figure 3

```

```

filter.c:

# include "filter.h"

void filter(

unsigned int size,

float * restrict imgMag, float * restrict imgPhase, // in & out

float *filterMag, float *filterPhase,

// in

// in

float *gaussian)

for(int idx = 0; idx < size; idx++)</pre>

{ // idx%3: RGB values from DC, first 3 elements of "filterMag"

imgMag[idx] /= (filterMag[idx] * 1/filterMag[idx%3] + filterMag[idx%3]);

imgMag[idx] *= gaussian[idx];

imgPhase[idx] -= filterPhase[idx];

}

Figure 4

```

"For large-scale systems like compute clusters, even small improvements are desirable—vector computation as a percore feature of the processor quickly amplifies through core and node count."

In C and C++, a pointer to a memory location is assumed to be overlapped by other pointers. Even strict ANSI aliasing rules, which prohibit reference of memory locations by pointers of different types, are not strict enough. They still allow pointers of the same type to overlap.

In our example, this is the case for all pointers. Hence the compiler has to assume dependencies among them. It should be emphasized that these are "assumed" dependencies, meaning they must not occur during runtime, and the compiler cannot disambiguate because the filter is implemented in a separate compilation unit. Nevertheless, any language-standard compliant compiler needs to assume the worst case—with pointers overlapping—and handle them correctly.

In most cases, such assumed dependencies may not be desired, and add unnecessary complexity to optimizations such as vectorization. However, for our example, every pointer from the parameter list references its own memory location. As a result these are not expected to overlap at all, which breaks up dependencies and increases the likelihood of successful vectorization. There are two ways to tell the compiler to ignore such assumed dependencies, the "restrict" keyword and the IVDEP pragma/directive.

### "Restrict" Keyword & IVDEP Pragma/Directive

The "restrict" keyword is a feature of the C99 standard. It can be attributed to pointers to guarantee that no other pointer overlaps the referenced memory location. Using the Intel® C++ compiler does not only limit it to C99. It makes the keyword available for C89 and even for different incarnations of C++, simply by enabling a dedicated option: "-restrict" (Linux\* and Mac OS\* X) or "/Qrestrict" (Windows\*).

**Figure 4** shows a possible implementation by using this keyword. It should be noted that we only need to apply the keyword to the two output parameters to break up the dependencies.

Another approach is the IVDEP pragma/directive, provided by all Intel compilers (C++ and Fortran). This pragma is used in front of block scopes, such as loops, to tell the compiler to ignore all assumed dependencies therein. Applied to our C example (Figure 5), the speedup is the same as with the "restrict" keyword (Figure 6). Nevertheless, the pragma still has some advantages over it. First, pragmas not known by other compilers are ignored. Thus this is less intrusive than using the keyword approach, which might not work for other compilers and non-C99 code. Second, the pragma can be used locally (e.g., for one loop), and leave the rest unchanged, while the keyword has impact on the entire function body. And lastly, the locality of the pragma allows it to selectively ignore overlapping memory locations. For example, it might be legal to ignore dependencies if certain conditions are met, but it would be incorrect to generally ignore these throughout the entire function body.

```

filter.c:

#include "filter.h"

void filter(

unsigned int size,

float *imgMag, float *imgPhase,

// in & out

float *filterMag, float *filterPhase, // in

float *gaussian)

// in

#pragma ivdep

for(int idx = 0; idx < size; idx++)</pre>

{ // idx%3: RGB values from DC, first 3 elements of "filterMag"

imgMag[idx] /= (filterMag[idx] * 1/filterMag[idx%3] + filterMag[idx%3]);

imgMag[idx] *= gaussian[idx];

imgPhase[idx] -= filterPhase[idx];

}

filter.f90:

subroutine filter(sze, imgMag, imgPhase, filterMag, filterPhase, gaussian) &

bind(C, name="filter")

use, intrinsic :: ISO C BINDING

implicit none

integer(kind=C INT), VALUE

real(C_FLOAT), dimension(*), intent(inout) :: imgMag

real(C_FLOAT), dimension(*), intent(inout) :: imgPhase

real(C_FLOAT), dimension(*), intent(in) :: filterMag

:: filterPhase

real(C_FLOAT), dimension(*), intent(in)

real(C_FLOAT), dimension(*), intent(in)

:: gaussian

:: idx

integer

! mod(idx, 3) + 1: RGB values from DC, first 3 elements of "filterMag"

!DEC$ IVDEP

do idx = 1, sze

imgMag(idx) = imgMag(idx) / (filterMag(idx) *

1/\text{filterMag}(\text{mod}(\text{idx}, 3) + 1) + &

filterMag(mod(idx, 3) + 1));

imgMag(idx) = imgMag(idx) * gaussian(idx)

imgPhase(idx) = imgPhase(idx) - filterPhase(idx)

end do

end subroutine

Figure 5

```

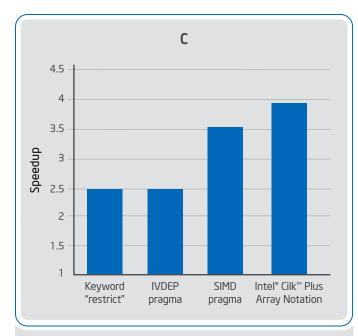

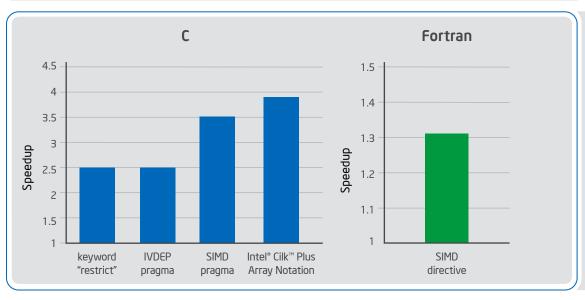

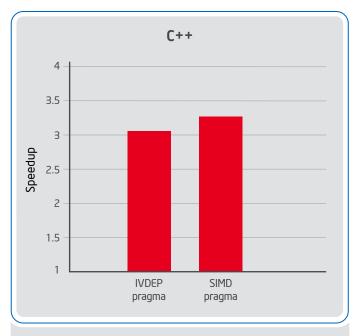

Figure 6: Speedup for the example against the baseline of the C version (higher is better)

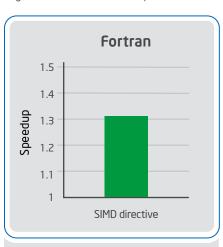

You might have noticed already that the result for the IVDEP directive (**Figure 5**) is not shown in **Figure 7**. That's true because Fortran is much stricter regarding overlapping memory regions than C, and because there's no improvement in our example. There are exceptions when using Fortran pointers.

Numerous other cases can also produce assumed dependencies for both C and Fortran. Two examples are access of array elements through indirection at runtime and conditional memory accesses in a loop. All such cases justify the availability of the IVDEP directive for Fortran as well.

In any case, both "restrict" keyword and IVDEP pragma/directive can change semantics of the code if applied incorrectly. For our example, both inform the compiler that no other pointer overlaps the referenced memory location. If this is violated, for instance, by sharing memory among different pointers of the function parameters, the compiler might reorder or otherwise optimize accesses in a way that yields

Figure 7: Speedup for the example against the baseline of the Fortran version (higher is better)

different results. Therefore, it is crucial to verify the correctness once the "restrict" keyword and IVDEP pragma/directive are used. In our case, we can do so easily by comparing the results of the different versions we have created. If the resulting image was corrupted, further analysis would be required. Since our example uses disjunctive memory locations, all optimizations work well.

### Intel® Cilk™ Plus SIMD Pragma/Directive

For the next step, we apply any of the above proposals to our C implementation. For the Fortran version, we still use the baseline. After consulting the vectorization report once again, vectorization still does not look optimal, for either the C or Fortran version (**Figure 8**):

It seems like the loop was not fully vectorized. This reflects the conclusion from the compiler's efficiency heuristic. It only regards a fraction of the loop body as being meaningfully vectorized. This result is based on general knowledge about the underlying architecture and on following language standards. Here, the compiler regards only a small fraction as not being vectorized, because of gather accesses caused by the modulo operations. There can be other cases where the compiler might not vectorize at all because of alleged inefficiency. In such cases there will be a clear message (**Figure 9**):

In such cases, it may make sense to ignore such heuristics, and also to partly ignore language standards to "enforce" vectorization. It should be noted that vectorization can only be enforced if it is technically possible. A loop which prints strings to the terminal is a trivial example which cannot be vectorized.

Intel Cilk Plus—an integral part of Intel compilers—comes with a SIMD pragma/directive that does what we are looking for: it ignores any compiler heuristic regarding efficiency, as well as any restrictions induced by the language to enforce vectorization. It also ignores all dependencies; not just assumed ones like the IVDEP pragma/directive. Due to this fact, it is important to mention that it can change semantics of vectorized code as a side effect. Hence, it is mandatory to verify the correctness once more. For our example, we simply compare the output among the different versions, as we already did for the changes with the "restrict" keyword and IVDEP pragma/directive.

Applying the SIMD pragma/directive to our example (**Figure 10**) indeed shows an additional improvement (**Figure 11**). Verifying the results also holds true; thus being a prime solution for us.

```

C:

filter.c(9): (col. 3) remark: PARTIAL LOOP WAS VECTORIZED.

filter.c(9): (col. 3) remark: PARTIAL LOOP WAS VECTORIZED.

Fortran:

filter.f90(13): (col. 3) remark: PARTIAL LOOP WAS VECTORIZED.

filter.f90(13): (col. 3) remark: PARTIAL LOOP WAS VECTORIZED.

Figure 8

```

remark: loop was not vectorized: vectorization possible but seems inefficient.

Figure 9

```

filter.c:

#include "filter.h"

void filter(

unsigned int size,

float * restrict imgMag, float * restrict imgPhase, // in & out

float *filterMag, float *filterPhase,

// in

float *gaussian)

// in

#pragma simd vectorlength(8) assert

for(int idx = 0; idx < size; idx++)</pre>

{ // idx%3: RGB values from DC, first 3 elements of "filterMag"

imgMag[idx] /= (filterMag[idx] * 1/filterMag[idx%3] + filterMag[idx%3]);

imgMag[idx] *= gaussian[idx];

imgPhase[idx] -= filterPhase[idx];

}

}

filter.f90:

subroutine filter(sze, imgMag, imgPhase, filterMag, filterPhase, gaussian) &

bind(C, name="filter")

use, intrinsic :: ISO_C_BINDING

implicit none

integer(kind=C_INT), VALUE

:: sze

real(C_FLOAT), dimension(*), intent(inout) :: imgMag

real(C_FLOAT), dimension(*), intent(inout) :: imgPhase

real(C_FLOAT), dimension(*), intent(in) :: filterMag

:: filterPhase

real(C_FLOAT), dimension(*), intent(in)

real(C_FLOAT), dimension(*), intent(in)

:: gaussian

integer

:: idx

! mod(idx, 3) + 1: RGB values from DC, first 3 elements of "filterMag"

!DEC$ SIMD VECTORLENGTH(8) ASSERT

do idx = 1, sze

imgMag(idx) = imgMag(idx) / (filterMag(idx) *

\frac{1}{\text{filterMag}(\text{mod}(\text{idx, 3}) + 1)} + &

filterMag(mod(idx, 3) + 1));

imgMag(idx) = imgMag(idx) * gaussian(idx)

imgPhase(idx) = imgPhase(idx) - filterPhase(idx)

end do

end subroutine

Figure 10

```

Figure 11

| Syntax                                                                            |                                                                                                                    |  |                                                                                             |  |  |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------------|--|--|--|

| C/C++: #pragma simd [clause[ [,] clause]] Fortran: cDEC\$ SIMD [clause[, clause]] |                                                                                                                    |  |                                                                                             |  |  |  |

| Arguments                                                                         |                                                                                                                    |  |                                                                                             |  |  |  |

| clause                                                                            | Can be any of the following:                                                                                       |  |                                                                                             |  |  |  |

|                                                                                   | <pre>vectorlength(n1[, n2])</pre>                                                                                  |  | Vector length to use (power of 2)                                                           |  |  |  |

|                                                                                   | vectorlengthfor(data type)                                                                                         |  | Only for C/C++; same as above but uses built-in types to calculate the vector length        |  |  |  |

|                                                                                   | <pre>private(var1[, var2]) firstprivate(var1[, var2]) lastprivate(var1[, var2]) reduction(oper:var1 [,var2])</pre> |  | Same as in OpenMP* work-sharing construct: see the OpenMP* 3.1 specification, section 2.5.1 |  |  |  |

|                                                                                   | <pre>linear(var1:step1       [,var2:step2])</pre>                                                                  |  | Specify additional induction variables                                                      |  |  |  |

|                                                                                   | [no]assert                                                                                                         |  | Compile time error in case vectorization fails                                              |  |  |  |